પરીક્ષણ કેપેસિટર્સ

કેપેસિટરના ઇન્સ્યુલેશન પ્રતિકારનું માપન. પાવર કેપેસિટરનું પરીક્ષણ કરતી વખતે, ઇન્સ્યુલેશન પ્રતિકાર ટર્મિનલ્સ વચ્ચે 2500 V ના વોલ્ટેજ માટે અને કેપેસિટર કેસની તુલનામાં મેગોહમિટર સાથે માપવામાં આવે છે. ઇન્સ્યુલેશન પ્રતિકાર અને ગુણોત્તર પ્રમાણિત નથી હું છું.

કેપેસિટરના ઇન્સ્યુલેશન પ્રતિકારનું માપન. પાવર કેપેસિટરનું પરીક્ષણ કરતી વખતે, ઇન્સ્યુલેશન પ્રતિકાર ટર્મિનલ્સ વચ્ચે 2500 V ના વોલ્ટેજ માટે અને કેપેસિટર કેસની તુલનામાં મેગોહમિટર સાથે માપવામાં આવે છે. ઇન્સ્યુલેશન પ્રતિકાર અને ગુણોત્તર પ્રમાણિત નથી હું છું.

અજમાયશ અવધિના કેપેસિટરોએ ઇન્સ્યુલેશનની ડાઇલેક્ટ્રિક તાકાતની ઔદ્યોગિક આવર્તનના વોલ્ટેજમાં વધારો કર્યો. ટેસ્ટ વોલ્ટેજ લાગુ કરવાની અવધિ 1 મિનિટ. ટેસ્ટ કેપેસિટરના કંડક્ટર અને કંડક્ટર અને હાઉસિંગ વચ્ચેના ઇન્સ્યુલેશન પર કરવામાં આવે છે. ટેસ્ટ વોલ્ટેજ કોષ્ટક અનુસાર લેવામાં આવે છે. 1.

કોષ્ટક 1. પ્રતિક્રિયાશીલ પાવર વળતર માટે કેપેસિટરના વોલ્ટેજનું પરીક્ષણ કરો

ટેસ્ટ પ્રકારો ટેસ્ટ વોલ્ટેજ, kV, ઓપરેટિંગ વોલ્ટેજ પર, kV 0.22 0.38 0.50 0.66 6.30 10.5 કેપેસિટર પ્લેટ્સ વચ્ચે 0.42 0.72 0.95 1.25 11.8 20 કન્ડેન્સરના સંદર્ભમાં.212153 કેસ. .3

કેપેસિટરના ટર્મિનલ્સ વચ્ચેના ઇન્સ્યુલેશનનું પરીક્ષણ કરતી વખતે પરીક્ષણ ટ્રાન્સફોર્મરની શક્તિ પ્રમાણમાં મોટી હોવી જોઈએ અને સૂત્ર દ્વારા નક્કી કરી શકાય છે:

પિસ્પ = ωCU2x 10 -9

જ્યાં P.internet પ્રદાતા — પાવર વપરાશ, kVA, C એ કેપેસિટરની કેપેસીટન્સ છે, pF, U — ટેસ્ટ વોલ્ટેજ, kV, ω — ટેસ્ટ વોલ્ટેજની કોણીય આવર્તન 50 Hz માં 314 જેટલી છે.

વોલ્ટેજમાં વધારો અને ઘટાડો સરળતાથી થવો જોઈએ. પર્યાપ્ત પાવરના ટેસ્ટ ટ્રાન્સફોર્મરની ગેરહાજરીમાં, વૈકલ્પિક વર્તમાન પરીક્ષણો કોષ્ટકમાં નિર્દિષ્ટ કરતા બમણા સમાન સુધારેલ વોલ્ટેજ પરીક્ષણ દ્વારા બદલી શકાય છે. 1 તણાવ.

ઔદ્યોગિક આવર્તન વધેલા વોલ્ટેજ પરીક્ષણો કેપેસિટર્સના ઇન્સ્યુલેશન કેસના સંબંધમાં કરવામાં આવશે નહીં જે બિડાણ સાથે જોડાયેલ ટર્મિનલ ધરાવતા પ્રતિક્રિયાશીલ શક્તિને વળતર આપવા માટે રચાયેલ છે.

પરીક્ષણ પછી, કેપેસિટર બેંકને વિશ્વસનીય રીતે વિસર્જિત કરવું આવશ્યક છે. ડિસ્ચાર્જ શરૂઆતમાં વર્તમાન મર્યાદિત અને પછી શોર્ટ-સર્કિટિંગ દ્વારા પરિપૂર્ણ થાય છે.

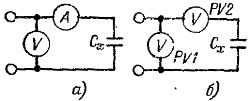

1000 V અને તેથી વધુના વોલ્ટેજ માટે પ્રતિક્રિયાશીલ શક્તિને વળતર આપવા માટે રચાયેલ કેપેસિટર્સ માટે કેપેસીટન્સ માપન ફરજિયાત છે. માપન 15 - 35 ° સે તાપમાને હાથ ધરવામાં આવવું જોઈએ. કેપેસિટર્સનું કેપેસિટેન્સ માપન એસી બ્રિજ, માઇક્રોફારાડોમીટર, એમીટર અને વોલ્ટમીટર પદ્ધતિ (ફિગ. 1, એ) અથવા બે વોલ્ટમીટર (ફિગ. 1, બી) નો ઉપયોગ કરીને ઉત્પાદિત.

ચોખા. 1. કેપેસિટરની ક્ષમતા માપવા માટેની યોજનાઓ: a — એમીટર અને વોલ્ટમીટર પદ્ધતિ દ્વારા, b — બે વોલ્ટમીટર પદ્ધતિ દ્વારા.

એમ્મીટર અને વોલ્ટમીટર વડે માપવામાં આવતી ક્ષમતાની ગણતરી સૂત્ર દ્વારા કરવામાં આવે છે:

Cx = (I x 106) / ωU,

જ્યાં Cx એ કેપેસિટરનું કેપેસીટન્સ છે, μF, I — માપેલ વર્તમાન, A, U — કેપેસિટરનું વોલ્ટેજ, V, ω — નેટવર્કની કોણીય આવર્તન 50 Hz પર 314 જેટલી છે.

એમ્મીટર અને વોલ્ટમીટર વડે કેપેસિટર્સની ક્ષમતાને માપતી વખતે, વોલ્ટેજ સિનુસોઇડલ હોવો જોઈએ. ઉચ્ચ હાર્મોનિક ઘટકોને કારણે વિકૃત વર્તમાન વેવફોર્મ સાથે, માપન ભૂલ નોંધપાત્ર રીતે વધે છે. તેથી, ફેઝ-ન્યુટ્રલ નેટવર્ક વોલ્ટેજને બદલે રેખીય રીતે માપન કરવાની ભલામણ કરવામાં આવે છે અને માપેલ કેપેસિટરની પ્રતિક્રિયાના આશરે 10% જેટલા સક્રિય પ્રતિકારને કેપેસિટર સાથે શ્રેણીમાં સર્કિટમાં શામેલ કરવાની ભલામણ કરવામાં આવે છે.

જ્યારે બે વોલ્ટમીટરથી માપવામાં આવે છે:

Cx = 106 / ωRtgφ,

R — વોલ્ટમીટરનો આંતરિક પ્રતિકાર, ઓહ્મ, tgφ — વોલ્ટમીટર U1 અને U2, cosφ = U2 / U1 ના વોલ્ટેજ વચ્ચેના કોણ φ તબક્કાના શિફ્ટના કોસાઇન દ્વારા નક્કી કરવામાં આવે છે.

સિંગલ-ફેઝ કેપેસિટર્સમાં, ક્ષમતાને ટર્મિનલ્સ વચ્ચે માપવામાં આવે છે, ત્રણ-તબક્કાના કેપેસિટર્સમાં - શોર્ટ-સર્કિટેડ ટર્મિનલની દરેક જોડી અને કોષ્ટક અનુસાર ત્રીજા ટર્મિનલ વચ્ચે. 2.

કોષ્ટક 2. ત્રણ-તબક્કાના કેપેસિટર્સની ક્ષમતાને માપવા માટેની યોજનાઓ

શોર્ટ સર્કિટ ટર્મિનલ્સ વચ્ચેની કેપેસીટન્સ માપો માપેલ કેપેસીટન્સ 2 અને 3 1 — (2 અને 3) C (1 — 2.3) 1 અને 3 2 — (1 અને 3) C (2 — 1.3) 1 અને 2 3 — (1 અને 2) C (3 - 1.2)

વાયર અને બોક્સ વચ્ચે કોઈ કેપેસીટન્સ માપન કરવામાં આવતું નથી. પિન નંબરિંગ મનસ્વી છે.

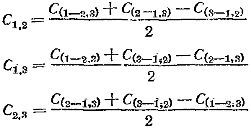

ડેલ્ટા-કનેક્ટેડ કેપેસિટરના દરેક તબક્કાની કેપેસિટેન્સ સમીકરણોમાંથી માપન ડેટા પરથી નક્કી કરવામાં આવે છે:

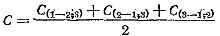

સંપૂર્ણ કેપેસિટર ક્ષમતા:

માપેલ ક્ષમતાઓ પાસપોર્ટ ડેટાથી 10% થી વધુ અલગ ન હોવી જોઈએ.

મેઇન્સ ઓપરેટિંગ વોલ્ટેજને ત્રણ વખત ચાલુ કરીને અને બેટરીના દરેક તબક્કામાં વર્તમાનને માપીને કેપેસિટર બેંકનું પરીક્ષણ કરો. જ્યારે કેપેસિટર બેંક ચાલુ હોય, ત્યારે કોઈ અસામાન્ય ઘટનાઓ અવલોકન ન કરવી જોઈએ (ઓટોમેટિક શટડાઉન, ફૂંકાયેલા ફ્યુઝ, ટાંકીમાં અવાજ અને ક્રેકીંગ વગેરે). બેટરીના વિવિધ તબક્કામાં પ્રવાહો એકબીજાથી 5% કરતા વધુ અલગ ન હોવા જોઈએ. નોમિનલના 110% કરતા વધુ વોલ્ટેજ માટે કેપેસિટર્સ શામેલ કરવા માટે પ્રતિબંધિત છે.