એન્ટિ-એલાઇઝિંગ ફિલ્ટર્સ અને વોલ્ટેજ સ્ટેબિલાઇઝર્સ

સ્મૂથિંગ ફિલ્ટર્સ રેક્ટિફાઇડ વોલ્ટેજ રિપલને ઘટાડવા માટે રચાયેલ છે. રિપલ સ્મૂથિંગનું મૂલ્યાંકન સ્મૂથિંગ ફેક્ટર q દ્વારા કરવામાં આવે છે.

સ્મૂથિંગ ફિલ્ટર્સ રેક્ટિફાઇડ વોલ્ટેજ રિપલને ઘટાડવા માટે રચાયેલ છે. રિપલ સ્મૂથિંગનું મૂલ્યાંકન સ્મૂથિંગ ફેક્ટર q દ્વારા કરવામાં આવે છે.

સ્મૂથિંગ ફિલ્ટર્સના મુખ્ય ઘટકો કેપેસિટર્સ છે, ઇન્ડક્ટર અને ટ્રાન્ઝિસ્ટર કે જેનો પ્રતિકાર પ્રત્યક્ષ અને વૈકલ્પિક પ્રવાહો માટે અલગ હોય છે.

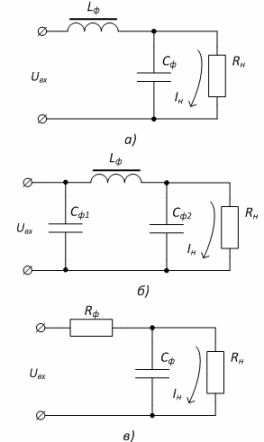

ફિલ્ટર તત્વના પ્રકાર પર આધાર રાખીને, કેપેસિટીવ, ઇન્ડક્ટિવ અને ઇલેક્ટ્રોનિક ફિલ્ટર્સ વચ્ચે તફાવત બનાવવામાં આવે છે. ફિલ્ટરિંગ લિંક્સની સંખ્યા અનુસાર, ફિલ્ટર્સને સિંગલ-લિંક અને મલ્ટિ-લિંકમાં વિભાજિત કરવામાં આવે છે.

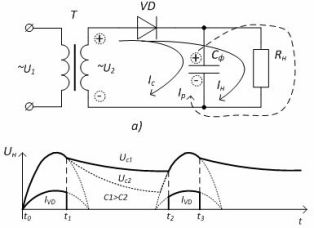

કેપેસિટીવ ફિલ્ટર એ મોટી ક્ષમતા ધરાવતું કેપેસિટર છે જે લોડ રેઝિસ્ટર Rn સાથે સમાંતર જોડાયેલ છે. કેપેસિટરમાં ઉચ્ચ ડીસી પ્રતિકાર અને ઓછી એસી પ્રતિકાર હોય છે. ચાલો હાફ-વેવ રેક્ટિફાયર સર્કિટ (ફિગ. 1, એ) ના ઉદાહરણ પર ફિલ્ટરની કામગીરીને ધ્યાનમાં લઈએ.

આકૃતિ 1-કેપેસિટીવ ફિલ્ટર સાથે સિંગલ-ફેઝ હાફ-વેવ રેક્ટિફાયર: a) સર્કિટ b) ઓપરેશનના સમય આકૃતિઓ

જ્યારે ટાઈમ ઈન્ટરવલ t0 — t1 (ફિગ. 2.63, b), લોડ કરંટ (ડાયોડ કરંટ) અને કેપેસિટર ચાર્જ કરંટ પ્રવાહમાં હકારાત્મક અર્ધ-તરંગ વહે છે.કેપેસિટર ચાર્જ થાય છે અને t1 સમયે કેપેસિટરમાં વોલ્ટેજ ગૌણ વિન્ડિંગના વોલ્ટેજ ડ્રોપ કરતાં વધી જાય છે — ડાયોડ બંધ થાય છે અને સમય અંતરાલમાં t1 — t2 કેપેસિટરના ડિસ્ચાર્જ દ્વારા લોડમાં વર્તમાન પ્રદાન કરવામાં આવે છે. ચે. લોડમાં વર્તમાન સતત વહે છે, જે સુધારેલા વોલ્ટેજની લહેરિયાંને નોંધપાત્ર રીતે ઘટાડે છે.

કેપેસિટર Cf ની કેપેસિટેન્સ જેટલી મોટી, ઉત્તેજના ઓછી. આ કેપેસિટરના ડિસ્ચાર્જ સમય દ્વારા નિર્ધારિત થાય છે — ડિસ્ચાર્જ સમય સ્થિર τ = СfRн. τ> 10 પર, સ્મૂથિંગ ગુણાંક ફોર્મ્યુલા q = 2π fc m Cf Rn દ્વારા નક્કી કરવામાં આવે છે, જ્યાં fc એ નેટવર્કની આવર્તન છે, m એ સુધારેલા વોલ્ટેજની અર્ધ-કાળની સંખ્યા છે.

ઓછી લોડ શક્તિઓ પર ઉચ્ચ પ્રતિકાર ધરાવતા આરએચ લોડ રેઝિસ્ટર સાથે કેપેસિટીવ ફિલ્ટરનો ઉપયોગ કરવાની ભલામણ કરવામાં આવે છે.

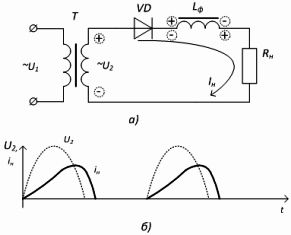

પ્રેરક ફિલ્ટર (ચોક) Rn (ફિગ. 3, a) સાથે શ્રેણીમાં જોડાયેલ છે. ઇન્ડક્ટન્સમાં નીચા ડીસી પ્રતિકાર અને ઉચ્ચ એસી પ્રતિકાર હોય છે. રિપલ સ્મૂથિંગ સ્વ-ઇન્ડક્શનની ઘટના પર આધારિત છે, જે શરૂઆતમાં વર્તમાનને વધતા અટકાવે છે, અને પછી તેના ઘટાડા સાથે તેને ટેકો આપે છે (ફિગ. 2, બી).

આકૃતિ 2-ઇન્ડેક્ટિવ ફિલ્ટર સાથે સિંગલ-ફેઝ હાફ-વેવ રેક્ટિફાયર: a) સર્કિટ, b) ઑપરેશનના ટાઇમિંગ ડાયાગ્રામ

ઇન્ડક્ટિવ ફિલ્ટર્સનો ઉપયોગ મધ્યમ અને ઉચ્ચ શક્તિના રેક્ટિફાયર્સમાં થાય છે, એટલે કે, મોટા લોડ પ્રવાહો સાથે કાર્યરત રેક્ટિફાયર્સમાં.

સ્મૂથિંગ ગુણાંક સૂત્ર દ્વારા નક્કી કરવામાં આવે છે: q = 2π fs m Lf / Rn

કેપેસિટીવ અને ઇન્ડક્ટિવ ફિલ્ટરનું સંચાલન એ હકીકત પર આધારિત છે કે નેટવર્ક દ્વારા વપરાશમાં લેવાતા વર્તમાનના પ્રવાહ દરમિયાન, કેપેસિટર અને ઇન્ડક્ટર ઊર્જા સંગ્રહિત કરે છે, અને જ્યારે નેટવર્કમાંથી કોઈ વર્તમાન નથી, અથવા તે ઘટે છે, ત્યારે તત્વો આપે છે. લોડમાં વર્તમાન (વોલ્ટેજ) જાળવી રાખીને સંગ્રહિત ઊર્જાનું શટડાઉન.

મલ્ટિ-જંકશન ફિલ્ટર્સ કેપેસિટર અને ઇન્ડક્ટર બંનેના સ્મૂથિંગ પ્રોપર્ટીઝનો ઉપયોગ કરે છે. લો-પાવર રેક્ટિફાયર્સમાં, જ્યાં લોડ રેઝિસ્ટરનો પ્રતિકાર ઘણા kOhm છે, ચોક Lf ને બદલે, રેઝિસ્ટર Rf શામેલ છે, જે ફિલ્ટરના સમૂહ અને પરિમાણોને નોંધપાત્ર રીતે ઘટાડે છે.

આકૃતિ 3 એલસી અને આરસી લેડર ફિલ્ટર્સના પ્રકારો દર્શાવે છે.

આકૃતિ 3-મલ્ટિ-જંકશન ફિલ્ટર્સ: a) L-આકારનું LC, b) U-shaped LC, c) RC-ફિલ્ટર

સ્ટેબિલાઇઝર્સ મુખ્ય વોલ્ટેજમાં વધઘટ અને લોડ દ્વારા વપરાશમાં આવતા પ્રવાહમાં ફેરફાર દરમિયાન લોડના સતત વોલ્ટેજ (વર્તમાન)ને સ્થિર કરવા માટે રચાયેલ છે.

સ્ટેબિલાઇઝર્સને વોલ્ટેજ અને વર્તમાન સ્ટેબિલાઇઝર, તેમજ પેરામેટ્રિક અને વળતરમાં વિભાજિત કરવામાં આવે છે. આઉટપુટ વોલ્ટેજની સ્થિરતાનું મૂલ્યાંકન સ્થિરીકરણ પરિબળ Kst દ્વારા કરવામાં આવે છે.

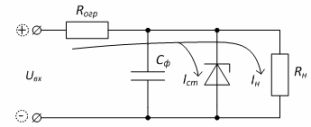

બિન-રેખીય લાક્ષણિકતા ધરાવતા તત્વના ઉપયોગ પર આધારિત પેરામેટ્રિક સ્ટેબિલાઇઝર - સેમિકન્ડક્ટર ઝેનર ડાયોડ. ઉપકરણ દ્વારા વિપરીત પ્રવાહમાં નોંધપાત્ર ફેરફાર સાથે ઝેનર ડાયોડનું વોલ્ટેજ લગભગ સ્થિર છે.

પેરામેટ્રિક સ્ટેબિલાઇઝર સર્કિટ આકૃતિ 4 માં બતાવવામાં આવ્યું છે. ઇનપુટ વોલ્ટેજ UBX મર્યાદિત રેઝિસ્ટર Rlim અને સમાંતર-જોડાયેલ ઝેનર ડાયોડ VD અને લોડ રેઝિસ્ટર Rn વચ્ચે વિતરિત કરવામાં આવે છે.

આકૃતિ 4 — પેરામેટ્રિક સ્ટેબિલાઇઝર

જેમ જેમ ઇનપુટ વોલ્ટેજ વધશે તેમ, ઝેનર ડાયોડ દ્વારા પ્રવાહ વધશે, જેનો અર્થ એ છે કે લિમિટીંગ રેઝિસ્ટર દ્વારા પ્રવાહ વધશે અને તેના પર મોટો વોલ્ટેજ ડ્રોપ થશે, અને લોડ વોલ્ટેજ યથાવત રહેશે.

પેરામેટ્રિક સ્ટેબિલાઇઝર પાસે 20-50 ના ઓર્ડરની Kst છે. આ પ્રકારના સ્ટેબિલાઇઝર્સના ગેરફાયદામાં નીચા સ્થિરીકરણ પ્રવાહો અને ઓછી કાર્યક્ષમતા છે.

પેરામેટ્રિક સ્ટેબિલાઇઝર્સનો ઉપયોગ સહાયક વોલ્ટેજ સ્ત્રોત તરીકે થાય છે, તેમજ જ્યારે લોડ પ્રવાહ નાનો હોય છે - સેંકડો મિલિએમ્પ્સ કરતાં વધુ નહીં.

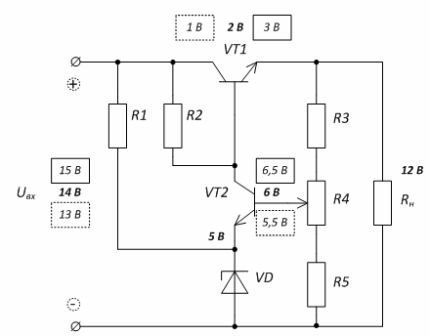

વળતર આપનાર સ્ટેબિલાઇઝર ટ્રાન્ઝિસ્ટરના ચલ પ્રતિકારનો ઉપયોગ મર્યાદિત રેઝિસ્ટર તરીકે કરે છે. જેમ જેમ ઇનપુટ વોલ્ટેજ વધે છે તેમ, ટ્રાન્ઝિસ્ટરનો પ્રતિકાર પણ વધે છે, અનુરૂપ, જેમ વોલ્ટેજ ઘટે છે, પ્રતિકાર ઘટે છે. આ કિસ્સામાં, લોડમાં વોલ્ટેજ યથાવત રહે છે.

ટ્રાન્ઝિસ્ટરનું સ્ટેબિલાઇઝર સર્કિટ આકૃતિ 5 માં બતાવવામાં આવ્યું છે. આઉટપુટ વોલ્ટેજ URn ના નિયમનનો સિદ્ધાંત નિયમન ટ્રાન્ઝિસ્ટર VT1 ની વાહકતામાં ફેરફાર પર આધારિત છે.

આકૃતિ 5 — વળતર આપનાર વોલ્ટેજ રેગ્યુલેટરની યોજનાકીય

ટ્રાન્ઝિસ્ટર VT2 પર વોલ્ટેજ સરખામણી સર્કિટ અને ડીસી એમ્પ્લીફાયર એસેમ્બલ કરવામાં આવે છે. માપન સર્કિટ R3, R4, R5 તેના બેઝ સર્કિટમાં શામેલ છે, અને સંદર્ભ વોલ્ટેજ સ્ત્રોત R1VD એમીટર સર્કિટમાં શામેલ છે.

ઉદાહરણ તરીકે, જેમ જેમ ઇનપુટ વોલ્ટેજ વધે છે તેમ, આઉટપુટ પણ વધશે, જે ટ્રાન્ઝિસ્ટર VT2 ના આધાર પર વોલ્ટેજમાં વધારો તરફ દોરી જશે, જ્યારે તે જ સમયે ઉત્સર્જક VT2 ની સંભવિતતા સમાન રહેશે.આનાથી બેઝ કરંટમાં વધારો થશે, અને તેથી ટ્રાન્ઝિસ્ટર VT2 નો કલેક્ટર કરંટ — ટ્રાન્ઝિસ્ટર VT1 ની બેઝ પોટેન્શિયલ ઘટશે, ટ્રાન્ઝિસ્ટર બંધ થશે અને તેના પર મોટો વોલ્ટેજ ડ્રોપ થશે, અને આઉટપુટ વોલ્ટેજ વધશે. યથાવત.

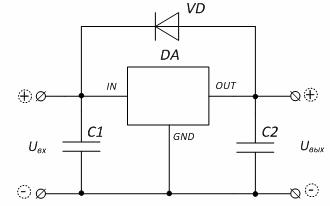

આજે, સ્ટેબિલાઇઝર્સ એકીકૃત સર્કિટના સ્વરૂપમાં ઉત્પન્ન થાય છે. એકીકૃત સ્ટેબિલાઇઝરને ચાલુ કરવા માટેની એક લાક્ષણિક યોજના આકૃતિ 6 માં બતાવવામાં આવી છે.

આકૃતિ 6 — બિલ્ટ-ઇન વોલ્ટેજ સ્ટેબિલાઇઝર ચાલુ કરવા માટે લાક્ષણિક યોજનાકીય

સ્ટેબિલાઇઝર માઇક્રોસર્ક્યુટના આઉટપુટનું હોદ્દો: «IN» — ઇનપુટ, «આઉટ» — આઉટપુટ, «GND» — સામાન્ય (કેસ). જો સ્ટેબિલાઇઝર એડજસ્ટેબલ છે, તો ત્યાં એક આઉટપુટ છે «ADJ» - ગોઠવણ.

સ્ટેબિલાઇઝરની પસંદગી આઉટપુટ વોલ્ટેજના મૂલ્ય, મહત્તમ લોડ વર્તમાન અને ઇનપુટ વોલ્ટેજની વિવિધતાની શ્રેણી પર આધારિત છે.